Программная архитектура Gigatron TTL microcomputer

Обзорно этот крайне забавный и минималистичный микрокомпьютер описан в предыдущей статье.

ЦП гигатрона обладает только одним 16–битным регистром: счётчиком инструкций (program counter — PC), все остальные регистры 8–битные.

Ввод–вывод осуществляется через регистры IN и OUT, аккумулятор AC хранит промежуточные результаты вычислений, регистры X и Y используются для расширенных режимов адресации, а при считывании 8–битного опкода очередной инструкции из плашки ПЗУ (гарвардская архитектура) в 64Кб из другой такой же плашки с такого же адреса считывается непосредственное 8–битное данное для инструкции и помещается в регистр D (data). Забавно, что многие команды не используют непосредственное данное и место в банке непосредственных данных в таком случае расходуется зря. ОЗУ образует отдельное адресное пространство от 32 до 64Кб. Стоит отметить, что в самой системе команд регистры IN и D доступны только для чтения, а регистры X, Y и OUT — только для записи.

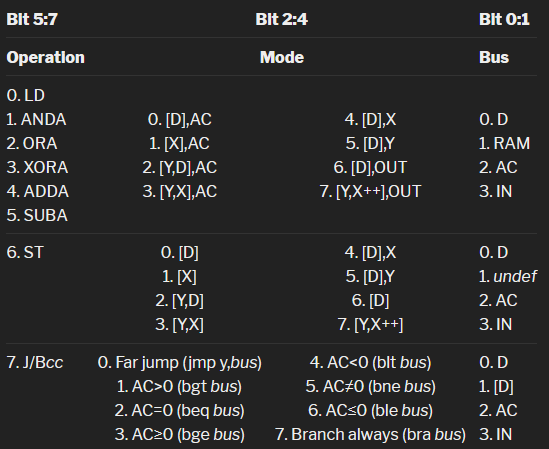

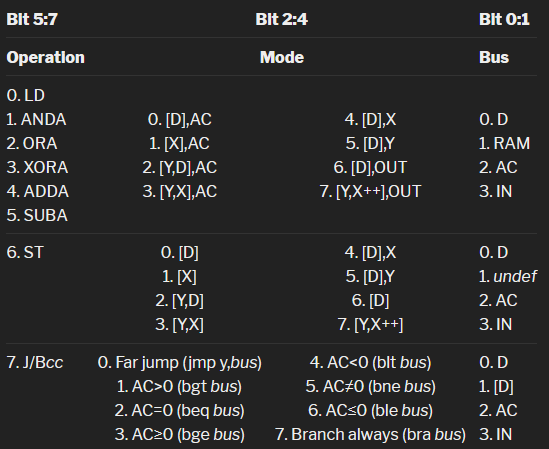

8–битный код инструкции разбит на 3 битовых поля: 3 бита на код операции, 3 бита на режим адресации или код условия и 2 бита на источник данных (шину).

Можно полностью описать все инструкции гигатрона следующей таблицей:

Как это работает: условно можно поделить все команды на три класса, что отражено в таблице. Давайте для начала рассмотрим инструкцию загрузки данных LD. Поле Bus описывает откуда данные загружаются — это или непосредственное данное D или аккумулятор AC или порт ввода IN или ОЗУ. Поле Mode описывает куда данное загружается — это AC, X, Y или OUT и в случае если в Bus выбрано считывание из памяти описывает режим адресации. В ассемблере пишется так: «LD откуда, куда», причём, если «куда» это аккумулятор, то он не пишется. Режимы адресации возможны следующие:

Заметьте, что автоматический инкремент X не распространяется на Y. X «проворачивается» через ноль не затрагивая Y, это надо учитывать.

Не все режимы адресации применимы ко всем регистрам–приёмникам — все корректные комбинации перечислены в таблице.

Немного примеров:

Арифметические инструкции ADDA, SUBA, ANDA, ORA, XORA работают почти так же как LD, но пропускают данное для загрузки через соответствующую операцию с аккумулятором, поэтому можно даже считать LD «холостой» арифметико–логической операцией. Например:

Во втором классе инструкций находится одна команда сохранения данных в память ST (store). В ней в поле Bus выбирается регистр который мы сохраняем в ОЗУ, а в поле Mode — один из вышеперечисленных режимов адресации. Забавным артефактом того, что в кишках гигатрона эти все операции приводятся в движение одними и теми же схемами является то, что если выбрать четвёртый или пятый режимы адресации (по таблице), то параллельно записи данного в память выполнится копирование аккумулятора в регистр X или Y. В ассемблере инструкция записывается преимущественно как «ST что, куда», при этом если «что» это аккумулятор, то он не пишется. Однако есть исключения с X и Y, см. ниже.

Примеры:

Обратите внимание, что вторая инструкция записывает непосредственное данное по тому же адресу, что и значение самого данного — иного не дано, т.к. D в инструкции может быть только один.

Забавно используется такая команда как ST D,[Y,X++] — в коде от авторов гигатрона можно встретить длинные цепочки этих инструкций — они как бы «переливают» блоки постоянных данных из ROM в ОЗУ.

Последний третий класс инструкций наполняют инструкции условных и безусловных переходов. В процессоре нет регистра флагов, поэтому все условия крутятся вокруг сравнения аккумулятора с нулём. Условие выбирается в поле Mode, при этом в поле Bus инструкции задаётся на что будет заменен нижний байт адреса в PC. То есть условные переходы возможны только в пределах одной 256–байтной страницы памяти. Одно из значений Mode означает «длинный безусловный переход», который помимо этого загружает в верхний байт PC значение из регистра Y и таким образом можно совершать «длинные» прыжки. Примеры:

Сам по себе счётчик инструкций инкрементируется как единое 16–битное целое и пересекает границы страниц без проблем.

Важно заметить, что в архитектуре компьютера реализован так называемый «delay slot» — следующая инструкция считывается процессором уже во время выполнения предыдущей, поэтому после выполнения перехода процессор обязательно исполнит сперва инструкцию которая лежала сразу за командой перехода.

Как замечают сами авторы — перед архитектурой гигатрона ставилась цель обеспечить побольше простоты железа мирясь с возрастанием сложности кода. Результатом является то, что у процессора крайне мало инструкций, отсутствует даже стек и битовые сдвиги приходится делать методом lookup–таблиц. Наверное это подтолкнуло их написать на гигатроне эмулятор 16–битного виртуального процессора с более полноценным набором инструкций и компилировать пользовательские программы уже для него.

ЦП гигатрона обладает только одним 16–битным регистром: счётчиком инструкций (program counter — PC), все остальные регистры 8–битные.

Ввод–вывод осуществляется через регистры IN и OUT, аккумулятор AC хранит промежуточные результаты вычислений, регистры X и Y используются для расширенных режимов адресации, а при считывании 8–битного опкода очередной инструкции из плашки ПЗУ (гарвардская архитектура) в 64Кб из другой такой же плашки с такого же адреса считывается непосредственное 8–битное данное для инструкции и помещается в регистр D (data). Забавно, что многие команды не используют непосредственное данное и место в банке непосредственных данных в таком случае расходуется зря. ОЗУ образует отдельное адресное пространство от 32 до 64Кб. Стоит отметить, что в самой системе команд регистры IN и D доступны только для чтения, а регистры X, Y и OUT — только для записи.

8–битный код инструкции разбит на 3 битовых поля: 3 бита на код операции, 3 бита на режим адресации или код условия и 2 бита на источник данных (шину).

Можно полностью описать все инструкции гигатрона следующей таблицей:

Как это работает: условно можно поделить все команды на три класса, что отражено в таблице. Давайте для начала рассмотрим инструкцию загрузки данных LD. Поле Bus описывает откуда данные загружаются — это или непосредственное данное D или аккумулятор AC или порт ввода IN или ОЗУ. Поле Mode описывает куда данное загружается — это AC, X, Y или OUT и в случае если в Bus выбрано считывание из памяти описывает режим адресации. В ассемблере пишется так: «LD откуда, куда», причём, если «куда» это аккумулятор, то он не пишется. Режимы адресации возможны следующие:

[D] — из непосредственного байтового адреса (zero–page)

[X] — по адресу из регистра X (zero–page)

[Y,D] — верхний байт адреса берется из Y, а нижний из D

[Y,X] — верхний байт адресе в Y, а нижний в X

[Y,X++] — то же что и [Y,X] с автоматическим инкрементом X после считыванияЗаметьте, что автоматический инкремент X не распространяется на Y. X «проворачивается» через ноль не затрагивая Y, это надо учитывать.

Не все режимы адресации применимы ко всем регистрам–приёмникам — все корректные комбинации перечислены в таблице.

Немного примеров:

LD 77 ; загрузит в AC константу 77

LD [77] ; загрузит в AC байт из адреса 77

LD AC, OUT ; запишет в порт вывода AC

LD [Y,X] ; загрузит в AC байт из адреса Y:XАрифметические инструкции ADDA, SUBA, ANDA, ORA, XORA работают почти так же как LD, но пропускают данное для загрузки через соответствующую операцию с аккумулятором, поэтому можно даже считать LD «холостой» арифметико–логической операцией. Например:

ADDA 77 ; AC=AC+77

ANDA [77], X ; X = ACC & RAM[77]

XORA [Y,X++],OUT ; OUT=ACC ^ RAM[Y:X]Во втором классе инструкций находится одна команда сохранения данных в память ST (store). В ней в поле Bus выбирается регистр который мы сохраняем в ОЗУ, а в поле Mode — один из вышеперечисленных режимов адресации. Забавным артефактом того, что в кишках гигатрона эти все операции приводятся в движение одними и теми же схемами является то, что если выбрать четвёртый или пятый режимы адресации (по таблице), то параллельно записи данного в память выполнится копирование аккумулятора в регистр X или Y. В ассемблере инструкция записывается преимущественно как «ST что, куда», при этом если «что» это аккумулятор, то он не пишется. Однако есть исключения с X и Y, см. ниже.

Примеры:

ST [77] ; RAM[77] = AC

ST 77, [77] ; RAM[77] = 77

ST IN, [77] ; RAM[77] = IN

ST [77], X ; RAM[77] = AC, X = AC

ST [Y,X++] ; RAM[Y:X] = AC, X = X + 1Обратите внимание, что вторая инструкция записывает непосредственное данное по тому же адресу, что и значение самого данного — иного не дано, т.к. D в инструкции может быть только один.

Забавно используется такая команда как ST D,[Y,X++] — в коде от авторов гигатрона можно встретить длинные цепочки этих инструкций — они как бы «переливают» блоки постоянных данных из ROM в ОЗУ.

Последний третий класс инструкций наполняют инструкции условных и безусловных переходов. В процессоре нет регистра флагов, поэтому все условия крутятся вокруг сравнения аккумулятора с нулём. Условие выбирается в поле Mode, при этом в поле Bus инструкции задаётся на что будет заменен нижний байт адреса в PC. То есть условные переходы возможны только в пределах одной 256–байтной страницы памяти. Одно из значений Mode означает «длинный безусловный переход», который помимо этого загружает в верхний байт PC значение из регистра Y и таким образом можно совершать «длинные» прыжки. Примеры:

JMP Y, 77 ; PC = 256 * Y + 77

BEQ IN ; если AC=0, то в нижний байт PC загружается INСам по себе счётчик инструкций инкрементируется как единое 16–битное целое и пересекает границы страниц без проблем.

Важно заметить, что в архитектуре компьютера реализован так называемый «delay slot» — следующая инструкция считывается процессором уже во время выполнения предыдущей, поэтому после выполнения перехода процессор обязательно исполнит сперва инструкцию которая лежала сразу за командой перехода.

Как замечают сами авторы — перед архитектурой гигатрона ставилась цель обеспечить побольше простоты железа мирясь с возрастанием сложности кода. Результатом является то, что у процессора крайне мало инструкций, отсутствует даже стек и битовые сдвиги приходится делать методом lookup–таблиц. Наверное это подтолкнуло их написать на гигатроне эмулятор 16–битного виртуального процессора с более полноценным набором инструкций и компилировать пользовательские программы уже для него.

0 комментариев